# The Liberty Simulation Environment: A Deliberate Approach to High-Level System Modeling

MANISH VACHHARAJANI, NEIL VACHHARAJANI, DAVID A. PENRY, JASON A. BLOME, SHARAD MALIK, and DAVID I. AUGUST Princeton University

In digital hardware system design, the quality of the product is directly related to the number of meaningful design alternatives properly considered. Unfortunately, existing modeling methodologies and tools have properties which make them less than ideal for rapid and accurate design-space exploration. This article identifies and evaluates the shortcomings of existing methods to motivate the Liberty Simulation Environment (LSE). LSE is a high-level modeling tool engineered to address these limitations, allowing for the rapid construction of accurate high-level simulation models. LSE simplifies model specification with low-overhead component-based reuse techniques and an abstraction for timing control. As part of a detailed description of LSE, this article presents these features, their impact on model specification effort, their implementation, and optimizations created to mitigate their otherwise deleterious impact on simulator execution performance.

Categories and Subject Descriptors: I.6.2 [Simulation and Modeling]: Simulation Languages; I.6.5 [Simulation and Modeling]: Model Development—Modeling methodologies; C.4 [Performance of Systems]: —Modeling techniques; I.6.7 [Simulation and Modeling]: Simulation Support Systems—Environments

General Terms: Design, Experimentation, Human factors, Languages Additional Key Words and Phrases: Liberty Simulation Environment (LSE), structural modeling, simulator construction, component reuse

#### 1. INTRODUCTION

In digital hardware system design, the quality of the product is directly related to the number of meaningful design alternatives properly considered. Since prototyping a candidate design is prohibitively expensive, designers rely instead on models to evaluate design alternatives. While analytical models have many desirable properties, current analytical modeling methods are only sufficient to provide accurate guidance for special cases. As a result, designers generally construct high-level (e.g. microarchitecture level) software simulation models for feedback.

In the computer architecture community, manually coding a simulator using a sequential language such as C or C++ is the most common method of producing a software simulation model<sup>1</sup>. Unfortunately, this methodology does not provide an *efficient* path to an *accurate*

Permission to make digital/hard copy of all or part of this material without fee for personal or classroom use provided that the copies are not made or distributed for profit or commercial advantage, the ACM copyright/server notice, the title of the publication, and its date appear, and notice is given that copying is by permission of the ACM, Inc. To copy otherwise, to republish, to post on servers, or to redistribute to lists requires prior specific permission and/or a fee.

<sup>&</sup>lt;sup>1</sup>In the 30th International Symposium on Computer Architecture in 2003, at least 23 of 37 papers used this

<sup>© 20</sup>YY ACM 0000-0000/20YY/0000-0001 \$5.00

### 2 · M. VACHHARAJANI et al.

simulation model. The methodology requires the designer to meticulously map the microarchitecture, which is inherently structural and concurrent, to a sequential programming language with functional composition. At best, this manual mapping is labor intensive and results in simulator code that does not conveniently convey architectural ideas. At worst, the simulator code is also difficult to understand and contains potentially serious errors that go unnoticed.

A common approach aimed at mitigating the problems with construction of these simulators is to reuse an existing, carefully constructed, and validated simulator for exploration of similar designs. The belief is that modifying a validated simulator will be easier and result in an accurate derivative. However, as this article will show, simulator modification suffers from the same problems as simulator construction; it is time-consuming and errorprone. Worse, the quality of the original is likely to lead one to a false sense of confidence in the derivative, resulting in only cursory validation, and permitting potentially serious errors to remain unnoticed.

The concurrent-structural approach is a different approach that eliminates the mapping problem by simply eliminating the manual mapping. This approach involves a language which allows designers to directly express the composition of the hardware in terms of components and static connections. Without the need to manually map, the modeling process is much less labor intensive. Since the model is a description of the hardware design, the model conveys architectural ideas, is easy for designers to understand, and exposes model/design mismatches.

Unlike in the manually-coded simulator approach, reuse is quite effective in the concurrent-structural approach. In concurrent-structural models, reuse at the component level is an attractive way to reduce model construction time [Swamy et al. 1995; Charest and Aboulhamid 2002] *and* improve accuracy. A component can be built and validated once and then used repeatedly, reducing modeling effort and potential sources of errors. The utility of such reuse is demonstrated by common hardware components such as queues and arbitration elements which can be used, unmodified, in vastly different hardware designs.

This article will show, however, that existing concurrent-structural modeling languages and tools force a trade-off between the ease of *building* reusable components and the ease of *using* such components. In current systems, this trade-off puts a high overhead on reuse, reducing reuse in practice, and thus negating its benefits. Further, one aspect of hardware design, timing control, does not benefit from reuse in concurrent-structural systems since timing control is non-local in nature, making it difficult to partition into one or more reusable model components. Consequently, in existing systems, users are forced to manually specify control for each design.

To address problems with existing systems and methodologies, we present the design and implementation of the Liberty Simulation Environment (LSE). To avoid the mapping problem, LSE is based around a concurrent-structural model specification language. Unlike existing concurrent-structural systems, LSE supports low overhead use *and* construction of reusable components through several programming language techniques. LSE is also the first system to provide an abstraction that simplifies the specification of timing control. Finally, LSE descriptions are statically analyzable enabling, for example, simulator construction optimizations to improve simulator execution performance and tools for automatic model visualization.

The remainder of this article is organized as follows. The first few sections carefully analyze existing systems to identify the root cause of their shortcomings. Section 2 explores in detail how the manual mapping of microarchitectures to sequential programs is slow and error-prone and why reuse cannot allow the cost of simulator development to be amortized. Section 3 analyzes systems that do not suffer from the mapping problem to determine why they still do not create an environment which encourages reuse. This analysis is then used to motivate the design of the Liberty Simulation Environment. Section 4 describes the Liberty Simulation Environment. Section 5 identifies the features that reduce component reuse overhead, and Section 6 describes LSE mechanisms to permit rapid specification of timing control. Section 7 discusses our experience with LSE and quantifies the reuse observed in practice. Sections 8, 9, and 10 describe novel approaches needed to implement the techniques discussed earlier in the article. Finally, Section 11 concludes by summarizing the contributions of this article.

#### 2. THE SEQUENTIAL MAPPING PROBLEM

To manage the design of complex hardware, designers divide the system's functionality into separate communicating hardware components and design each individually. Since each component is smaller than the whole, designing the component is significantly easier than designing the entire system. If components are too complex, they too can be divided into sub-components to further ease the design process. The final system is built by assembling the individually designed components. To ensure the components will interoperate, designers, when dividing the system, agree on the communication interface of each component. This interface, which defines what input each component requires and what output each component will produce, encapsulates the functionality of each component; other parts of the system can change without affecting a particular component provided its communication interface is respected. We call this type of encapsulation and communication structural composition.

Leveraging encapsulation to allow this divide-and-conquer design strategy is also very common in software design. Sequential programming languages such as C or C++ use functions to encapsulate functionality. Each function has a communication interface (its arguments and return value) and this interface encapsulates the function's behavior. Software systems are built by assembling functions which communicate by calling one another and passing arguments and receiving return values. We call this type of encapsulation and composition *functional composition*.

The presence of encapsulation combined with designer familiarity and tool availability make sequential programming languages seem like a natural tool with which to model hardware systems. However, as will be seen in this section, the encapsulation permitted by functional composition in sequential languages is not the same as the encapsulation provided by structural composition. This mismatch forces designers to *map* their structurally composed hardware designs to functionally composed sequential programming languages. This section demonstrates that this mapping is time-consuming, error-prone, and yields simulators that are difficult to understand and hard to modify. Thus we can conclude that, despite the popularity of this methodology, manually coding hardware models in sequential languages is ill-suited for design space exploration.

The discussion of the *mapping problem* proceeds as follows. Section 2.1 describes why simulators built using sequential languages (*sequential simulators*) are hard to build, diffi-

#### M. VACHHARAJANI et al.

cult to understand and thus, prone to error. Section 2.2 presents empirical data supporting this claim. Section 2.3 explains why building a new simulator by modifying an existing one is difficult, illustrating that the cost of building and validating simulators cannot be amortized across many designs during exploration. Section 2.4 presents empirical data supporting this claim.

# 2.1 Simulator Construction and the Mapping Problem

When dividing a complex hardware design into simpler components, designers choose a partitioning that allows them to most easily understand the design. Often this partitioning forms the vocabulary that designers use to think about and discuss the design. Consequently, the easiest simulator to build and understand would share this same partitioning. Unfortunately, differences between the styles of encapsulation used in hardware and sequential programming languages prevent this. As will be described in this section, when mapping from hardware components to software functions, the encapsulation provided by the hardware components must be broken forcing the designer to reason about many components simultaneously. This reasoning, and therefore the mapping, is laborious and extremely time consuming. Further, since the encapsulation of code in the simulator is not representative of the hardware, understanding how a simulator written in a sequential language models hardware is also difficult. Ultimately, modeling hardware in a sequential language hides pieces of a component's interface, intertwines computation and communication, and requires manual orchestration of concurrency.

A fundamental attribute of the encapsulation provided by hardware is the explicit specification of interfaces and the clear separation between functionality and communication. A hardware component will typically define its communication interface as a collection of ports through which it receives input and sends output. The component will define its behavior by specifying how it translates data arriving at its input ports to data it will send to its output ports. Independent of this specification of interface and behavior, the communication of the system is determined by the connectivity of its components' ports. A particular component may receive input from one or more other components and similarly, may send its output to one or more recipients.

The encapsulation provided by functions in sequential programming languages seems similar. The arguments to the function seem to mirror a component's input ports, and the return value seems to mirror the output ports. The body of the function specifies its behavior as a translation from inputs to outputs. Unfortunately, calling a function from within the body of another function implicitly augments the communication interface of the caller and intertwines functionality with communication. The arguments sent to the callee and the return value received from it are additional *implicit* outputs and inputs of the caller. Further, the recipient of data sent and the sender of data received from this augmented interface is determined by the function being called. Unlike structural composition, a function must receive all of its arguments from a single caller and send all of its outputs back to that same caller. Therefore, the arbitrary and independently specified communication patterns provided by structural composition are absent when using functional composition.

An alternate style of modeling hardware in a sequential programming language uses global variables, as opposed to function arguments and return values, to communicate information through the system. Unfortunately, in such systems, the problems discussed above still exist. The communication interface of a particular function is still implicitly specified through its behavior specification. Each global variable accessed defines a piece

```

foreach simulation cycle

foreach simulation cycle

do commit stage

do commit stage

do writeback stage

do writeback stage

do ex stage

do ex stage

do issue stage

5

do issue stage

do fetch stage

do fetch stage

foreach instr[i]

8

if instr[i].issued

dequeue instr[i]

(a) original main simulator loop

(c) modified main simulator loop

Issue Logic

instr[1..n] = first n instructions in queue

instr[1..n] = first n instructions in queue

for each instr[i] that was fetched

for each instr[i] that was fetched

if instr[i] is a branch

if instr[i] is a branch

fetch source registers

4

fetch source registers

5

5

if branch unit is available

if branch unit is available

compute the target PC

compute the target PC

issue instruction to the branch unit

issue instruction to the branch unit

dequeue instr[i]

if instr[i] is an ALU op

instr[i].issued=TRUE

if instr[i] is an ALU op

10

11

12

fetch source registers

fetch source registers

If ALU is available

11

If ALU is available

issue instruction to the ALU

12

issue instruction to the ALU

13

13

instr[i].issued=TRUE

dequeue instr[i]

(b) original issue stage

(d) modified issue stage

```

Fig. 1. Sequential simulator code.

of the function's communication interface. Further, the behavior and communication of a function are still intertwined since two functions communicate if one writes to a global variable that the other reads. Furthermore, when using global variables, even the specification of communication is implicit, unlike in the previous style. The target of communication is never explicitly specified but implied by analyzing how data flows through global variables. Two functions may appear to communicate because they access the same global variable, but a third function may overwrite the global variable after the first has written it but before the second has consumed the data. Careful examination is required to truly understand the communication present in such systems.

The implicit communication when using global variables reveals another shortcoming of the encapsulation provided by functional composition. Components in a hardware system execute *concurrently* with one another. If a component has sufficient input to perform a computation, it will proceed without waiting for additional input. With sequential programming languages and functional composition, however, the interactions between components must be manually orchestrated by sequencing function invocation. Sequencing these invocations may not be straightforward. For example, when using global variables to communicate, interchanging the order in which two functions are called can cause data to be delayed by a cycle or can even change the communication pattern. Great care must be taken to ensure the proper sequence is specified. Worse still, if functions have not been appropriately partitioned, there may be no correct order of invocation. For example, if component A generates output that feeds component B, and an output of component B feeds component A, then no order of invocation between A and B will work. The functions would need to be partitioned so that the new functions could be scheduled.

The problems discussed above are all manifestations of the mapping problem. To see how this problem can occur in practice, consider the following example. Figure 1(a) shows a typical main simulation loop for a sequential simulator that models a typical five stage superscalar processor pipeline. The hardware is modeled using a function per pipeline stage. The functions communicate through global variables, which effectively model the pipeline registers between the stages. Since later pipeline stages wish to use data produced from previous cycles, they must run before the global variables get overwritten by earlier stages. Therefore, the main simulator loop begins computation at the back of the pipe and moves toward the front so that later pipeline stages use state from previous cycles, before earlier stages overwrite the data. This invocation order also allows back-pressure to flow through the pipe. If a stage later in the pipeline stalls, it can set a global variable to inform earlier stages of the stall.

We now focus on the issue stage of the pipeline, whose code is shown in Figure 1(b). From the pseudo-code we see that when an instruction is sent to its functional unit, it is simultaneously removed from the instruction window (lines 7-8 and 12-13 in Figure 1(b)). When the fetch stage (the stage that places instructions into the instruction window) is executed, the newly created space will be available for new instructions.

Now, suppose that the designers would like to model a different behavior in which freed slots in the instruction window are not available until the cycle after the instruction was issued. Such a behavior may be desirable if, for example, the dequeue signals would arrive too late in the cycle with the original behavior. The hardware differences between the original and the new behavior simply amount to removing the dequeuing logic from the computation of a control signal indicating the number of slots available. Figures 1(c) and 1(d) show the necessary changes to the simulator main loop and issue logic, respectively, to model the new behavior.

Notice that the sequential simulator code that models two very similar architectures contains significant differences. These differences are indicated by the bars to the right of the line numbers in Figure 1. Specifically, the change to the microarchitecture required partitioning of code for the issue logic and the addition of new simulator state to allow the pieces of the issue logic to communicate. The code to dequeue instructions from the instruction window had to be separated from the code that dispatched instructions to the functional units since these two events occur at different times in the modified hardware design. The majority of the issue logic remains in the issue stage function, but some of the logic is now intermingled with the code that schedules the execution of the pipeline stages (lines 7-9 in Figure 1(c)). The modified code also needs an additional global variable to maintain the issued status for each issue window slot so that the piece of the issue logic that dequeues instructions knows which instructions were issued.

Just as changing instruction window timing required partitioning a logical entity in the hardware into different functions in the simulator model, other microarchitecture features may also force undesirable partitioning. While this small example may not seem overwhelming, this kind of partitioning is very common throughout the code for sequential simulators. Because of this, sequential simulator authors need to carefully plan how hardware component functionality needs to be partitioned, decide what global state will be used for communication, and carefully orchestrate the invocation of functions to ensure that all global state is updated in the correct sequence.

Notice that this mapping process can be extremely complicated and therefore difficult to perform correctly. Since mistakes can easily be made, the resulting simulator needs to be carefully checked to ensure correctness. Correctness is usually determined by testing each component as a unit and then testing the composed whole. In the best case, the entire

model will be built by reusing pre-validated components. As we have seen, however, the mapping process breaks structural encapsulation, thus making component testing and component-based reuse impossible. Even components commonly thought of as testable units in a sequential simulator, such as a cache component, are not independently testable since, to allow correct modeling of timing, they are often tightly coupled to the whole simulator [Desikan et al. 2001].

Sequential simulators are also difficult to manually validate as a whole. Designers understand the hardware in terms of hardware components and their communication. A strict separation of computation, communication, and operation sequencing is critical to the understanding of a hardware design. As seen above, however, the way in which a sequential simulator is built breaks component encapsulation and intermingles communication and computation. Furthermore, recall that with sequential simulators communication between code that models hardware blocks is often implicit. This makes the resulting simulator difficult to understand and thus difficult to manually validate. This in turn makes an *accurate* simulator even more difficult and time-consuming to build.

#### 2.2 Simulator Construction and the Mapping Problem: Model Clarity

The previous discussion gives intuition as to why accurate sequential simulators are difficult to build. Correctness is especially hard to ensure because the simulator is very hard to understand. The experiment presented in this section supports the claim that sequential simulators are difficult understand and thus difficult to validate.

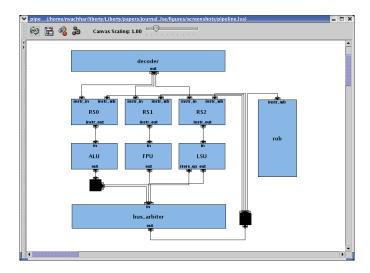

To quantify the clarity of sequential simulators, a group of subjects was asked to examine sequential simulator code modeling a microprocessor and identify properties of the machine modeled. As a reference point, the subjects were asked *exactly* the same questions for a model of a similar machine built in the Liberty Simulation Environment (LSE). As described in detail later, LSE is a hardware modeling framework in which models are built by connecting concurrently executing software blocks much in the same way hardware blocks are connected. Thus, LSE models closely resemble the hardware block diagrams of the machines being modeled. We call these structurally composed models *structural models* to distinguish them from functionally composed *sequential simulators*.

Subjects received different versions of the machine models to ensure that the effects observed were not a due to a particularly difficult to understand hardware policy. The sequential simulators used were a collection of modified and unmodified versions of sim-outorder.c from version 3.0 of the popular SimpleScalar tool [Burger and Austin 1997]. sim-outorder.c models a superscalar machine that executes the Alpha instruction set. The LSE models were variations of a superscalar processor model that executed the DLX instruction set. A refined version of this model was released along with the Liberty Simulation Environment in the package tomasulodlx [The Liberty Research Group].

To ensure that the experiment measured the quality of the model, not the knowledge of the subjects, all the subjects were either Ph.D. students studying computer architecture or Ph.D. holders whose primary work involved computer architecture. To ascertain the background of subjects, each was given a questionnaire to determine their familiarity with computer architecture, programming languages, and existing simulation environments, particularly, SimpleScalar. A summary of the answers to this questionnaire is in Table I.

Note that finding qualified subjects unaffiliated with the Liberty Research Group for this experiment was challenging given our requirements. Subjects had to be very familiar with

|         | Years        | Wrote     | Wrote     | Years      | Days       |              |

|---------|--------------|-----------|-----------|------------|------------|--------------|

|         | in           | a C       | RTL for a | Experience | Experience | Used         |

| Subject | Architecture | Simulator | CPU Core  | w/ C/C++   | w/ LSE     | SimpleScalar |

| S1      | 3            | Yes       | No        | 5          | 3          | Yes          |

| S2      | 10           | Yes       | Yes       | 15         | 2          | No           |

| S3      | 3            | No        | Yes       | 5          | 2          | No           |

| S4      | 3            | No        | No        | 6          | 3          | Yes          |

| S5      | 3            | No        | No        | 7          | 3          | No           |

| S6      | 3            | Yes       | Yes       | 6          | 3          | Yes          |

| S7      | 3            | No        | Yes       | 8          | 3          | Yes          |

| S8      | 3            | No        | No        | 5          | 4          | No           |

| S9      | 2            | No        | No        | 14         | 5          | No           |

| S10     | 6            | Yes       | No        | 10         | 5          | Yes          |

Table I. Subject responses to the questionnaire.

computer architecture and also had to be familiar with LSE. The second constraint proved to be the most difficult given that LSE is a relatively new system. Thus, only ten subjects were available for this experiment. As will be seen, however, even with ten subjects the results are quite dramatic.

Each subject was given 90 minutes to answer 2 multi-part questions for the sequential SimpleScalar simulator and the same questions for the structural LSE model along with 4 control questions. The control questions were asked first. Following these questions, each multi-part question for the sequential simulator was asked immediately after the same question for the structural model. The questions (with placeholders for line numbers and filenames) are shown in Appendix  $A^2$ .

The control questions were used to determine if the subjects had basic familiarity with LSE since each had less than one week of experience with the tool. The answers to the control questions indicated that all subjects understood LSE enough for the purposes of this experiment.

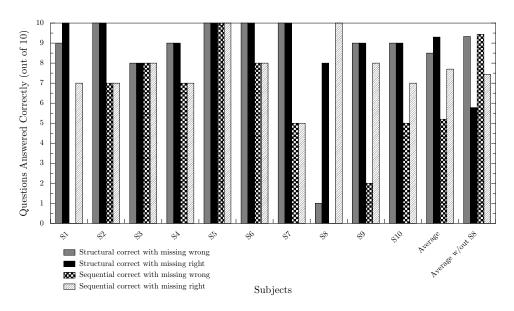

Figure 2(a) summarizes the results. Since the subjects had limited time, not all subjects could answer all questions. The first pair of bars corresponds to responses regarding the structural model. The first bar in the pair assumes that all questions left unanswered were answered incorrectly. The second bar in the pair of bars shows the same data assuming that all unanswered questions were answered correctly. The second pair of bars shows the same information for questions regarding the sequential simulator. From the graph, we can see that in each case subjects were able identify the machine properties at least as accurately with the structural model as they were with the sequential simulator, usually much more accurately. On average, subjects answered 8.5 questions correctly with the structural model versus 5.2 for the sequential model. Even if unanswered questions are assumed correct for only the sequential simulator, almost all subjects answered more questions correctly with the structural model. The only subject who does better with the sequential simulator, under these circumstances, is subject S8, who spent an unusually long time on the control questions and thus did not have time to answer any questions regarding the sequential simulator. In fact, S8 only completed the first two parts of the first non-control question for the structural model (questions 1(a) and 1(b) as numbered in Appendix A) and no questions

$<sup>^{2}</sup>$ More details regarding the questions and machine models are available in the references [Vachharajani and August 2004].

(a) Number of correctly answered questions, by subject.

(b) Total time taken for each group of questions, by subject.

Fig. 2. Results of the simulator clarity experiment.

10

for the sequential simulator. Clearly subject S8 is an outlier.

If subject S8 is excluded from the data, we see that, on average, 9.33 questions were answered correctly for the structural model versus 5.78 for the sequential simulator. Even when unanswered questions are assumed correct for the sequential simulator and incorrect for the structural model, the structural model still has 9.33 correctly answered questions versus 7.44 for the sequential simulator. These averages are statistically significant<sup>3</sup>.

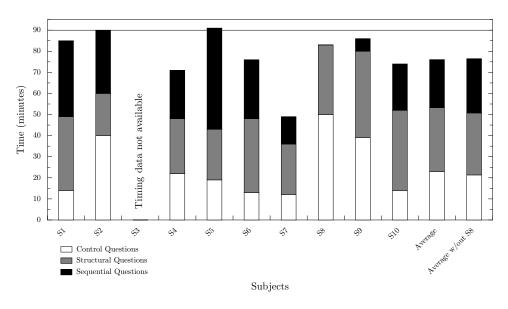

Figure 2(b) summarizes the time taken to answer each class of questions: control questions, questions for the structural model, and questions for the sequential model. With S8 excluded, the average time taken per question for the structural model differs by only 30 seconds when compared to the time for questions about the sequential simulator. Therefore, the increased number of correct responses for the structural model is not due to substantially more time spent on those questions. Note that the total times are typically below 90 minutes since the time taken for any breaks was not counted. Subject S7 completed the questions extremely quickly, hence the short bar. Subject S3 failed to provide complete timing information.

Note that the experiment is skewed in favor of the sequential simulator. First, since subjects were asked the LSE question immediately before being asked the same question for the sequential simulator, subjects could use the hardware-like model to understand what to look for in the sequential simulator. Second, many of the subjects were familiar with the stock sim-outorder.c simulator. Third, all subjects had many years of experience using the C language (the language used for sim-outorder.c) and less than a week of experience with LSE (the tool used to build the structural model). Fourth, no subject had ever seen a full LSE processor model before the experiment. Finally, the testing environment did not permit subjects to use the LSE visualization tool to graphically view block diagrams of the structural specification. In our experience, this tool significantly simplifies model understanding; subject responses to the questions indicated that much of their time answering questions about the structural model was spent drawing block diagrams. Despite all this, the results clearly indicate that sequential simulators are significantly more difficult to understand.

# 2.3 Reuse and the Mapping Problem

A tempting approach to allow rapid construction of simulation models in the face of the previously described difficulties is to amortize the cost of model construction via wholemodel reuse. In this approach, a sequential simulator is built once, validated versus a "golden" reference, such as real hardware, and then modified to model a new design. Since the new model is a modification of a validated model, the belief is that the likelihood of error is reduced and modeling efficiency is increased. However, this is not the case. Sequential simulators are not only difficult to build and understand, but also difficult to modify correctly.

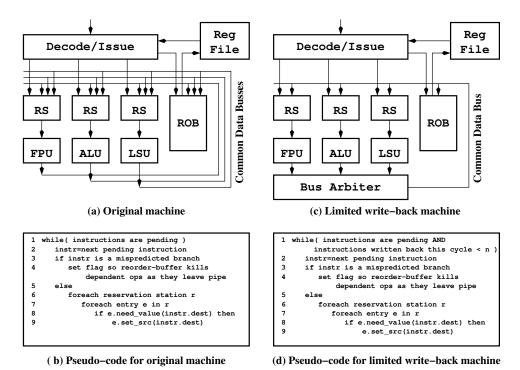

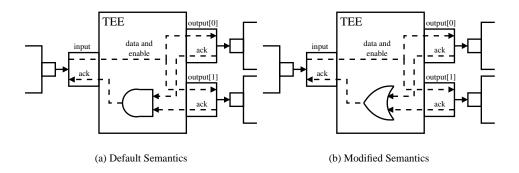

To see why these simulators are difficult to modify correctly, consider a simulator, written in the same style as the one in Figure 1, which models a machine that uses Tomasulo's dynamic scheduling algorithm. Figure 3 presents a block diagram of such a machine and shows the code for the writeback stage of the pipeline. The code iterates over all instructions that have completed execution and updates the dependency information of instructions pending execution. While the code seems to model the hardware reasonably well,

$<sup>^3</sup>$ The probability of a Type I error (the p-value in statistics) is 0.004

Fig. 3. The structure and pseudo-code for two Tomasulo-style machines.

closer examination reveals that this machine has unrestricted writeback bandwidth; any instruction that has completed execution will be written back.

Limiting the writeback bandwidth seems simple. One need only modify the loop termination condition to cause the loop to exit if the writeback bandwidth has been exceeded. Figure 3(d) shows this modified code. Careful inspection, however, reveals that this one line code modification has had unexpected results. The functional units which will be able to successfully write back results to the writeback buses is determined by the order that the while loop (line 1 in Figure 3(d)) processes the requests. Thus, as shown in Figure 3(c), the sequential semantics of the programming language used during modeling has *implicitly* introduced a bus arbiter that is not *explicitly* modeled by the code.

Worse still, the arbiter's exact functionality depends on *simulator state* that does not correspond to any *microarchitectural state*. The order in which the simulator iterates over the instructions in the while loop determines which instructions are written back. Prior to this modification, the iteration order was irrelevant. Now, the iteration order determines the behavior of the microarchitecture and this order is not necessarily determined in any one place in the simulator's code. For example, the iteration order can be affected by the order in which functional units are processed (which is often arbitrary) or the specific implementation of the data structure used to store the instructions waiting to write back. Thus, this small change breaks the encapsulation of the writeback stage allowing seemingly irrelevant implementation details to affect simulation results.

12

Configuration Name | Configuration Description |

mispred\_imm | Force all branches to resolve immediately in the writeback stage |

Force all branches to resolve in order in the writeback stage |

Force all branches to resolve in order in the commit stage |

Force all branches to resolve in order in the commit stage |

Force all branches to resolve in order in the commit stage |

Force all branches to resolve in order in the commit stage |

Force all branches to resolve in order in the commit stage |

Force all branches to resolve in order in the commit stage |

Force all branches to resolve in order in the writeback stage |

Force all branches to resolve in order in the writeback stage |

Force all branches to resolve in order in the writeback stage |

Force all branches to resolve in order in the writeback stage |

Force all branches to resolve in order in the writeback stage |

Force all branches to resolve in order in the writeback stage |

Force all branches to resolve in order in the writeback stage |

Force all branches to resolve in order in the commit stage |

Force all branches to resolve in order in the writeback stage |

Force all branches to resolve in order in the commit stage |

Force all branches to resolve in order in the writeback stage |

Force all branches to resolve in order in the commit stage |

Force all branches to resolve in order in the writeback stage |

Force all branches to resolve in order in the writeback stage |

Force all branches to resolve in order in the writeback stage |

Force all branches to resolve in order in the writeback stage |

Force all branches to resolve in order in the writeback stage |

Force all branches to resolve in order in the writeback stage |

Force all branches to resolve in order in the writeback stage |

Force all branches to resolve in order in the writeback stage |

Force all branches to resolve in order in the writeback stage |

Force all branches to resolve in order in the writeback stage |

Force all branches to resolve in order in the writeback stage |

Force all branches to r

Table II. Descriptions of the modeled microarchitectural variants.

Table III. Time spent and code changed for modifications from the baseline configuration.

|               | LSE Model |                  |        | Sequential Model |                    |         |

|---------------|-----------|------------------|--------|------------------|--------------------|---------|

| Configuration | diff/wc   | Modules Affected | Time   | diff/wc          | Functions Affected | Time    |

| mispred_imm   | 146       | 8                | 1.5hrs | 400              | 16                 | 5 hrs   |

| mispred_old   | 165       | 9                | 45 min | 413              | 16                 | 1.5 hrs |

| mispred_com   | 177       | 10               | 15 min | 629              | 17                 | 15 min  |

| delaydec      | 16        | 1                | 15 min | 94               | 6                  | 2 hrs   |

| splitda       | 124       | 5                | 40 min | N/A              | N/A                | > 5 hrs |

| splitruu      | 13        | 1                | 36 min | 50               | 7                  | 3 hrs   |

# 2.4 Reuse and the Mapping Problem: Simulator Modification Time

To show that correctly modifying a sequential simulator is unnecessarily difficult and time consuming, an experiment that gauges how rapidly an existing simulator could be *correctly* modified was conducted. Specifically, a subject was asked to perform various modifications to a sequential simulator and to an equivalent model whose specification more closely resembles hardware. The requested modifications are shown in Table II. The sequential simulator modified by the subject was the SimpleScalar 3.0 sim-outorder.c simulator. The model that more closely resembles hardware was once again built with the Liberty Simulation Environment (LSE). The base LSE model and the base sim-outorder simulator <sup>4</sup> that were modified in the experiment had exactly matching pipeline traces. At the time this experiment was conducted the subject had little experience with both LSE and SimpleScalar. To ensure correctness of the modified models, each pair of modified models' output was carefully checked by hand and against each other. The subject had to resolve any discrepancies between pipeline traces generated by the two models.

In order to evaluate how difficult it was to correctly modify the sequential simulator, three metrics were used to compare the sequential model to the LSE model. The first metric, the diff/wc metric, measured how much a specification deviated from the base specification by counting the number of lines in a diff between the original and modified configuration. The second metric captured the locality of the changes necessary to move from an initial architectural model to a modified one. Since the specifications of the two simulators being compared are different, a hand count of the number of components affected in the LSE model was compared to a hand count of the number of C functions modified for SimpleScalar. The final metric used was a timing of how long each particular modification took. Any time required to resolve discrepancies between the output of two models was charged to the model that was deemed to be incorrect.

$<sup>^4</sup>$ The base  ${\tt sim-outorder.c}$  model had a few patches applied to fix bugs in the stock model.

The results of the experiment are summarized in Table III. Note that the splitda modification could not be completed in the sequential model in under five hours and was abandoned. Across the board, it took less time and fewer modifications to build the LSE model when compared to the hand-coded sequential C simulator. Furthermore, the changes were more local in the LSE specification than they were in SimpleScalar. These results clearly indicate that sequential models are unnecessarily time-consuming to modify given that the LSE models can be used to automatically generate simulators. Note that in each case where there was a discrepancy, inspection revealed that the sequential model was the one that contained the error. This lends support to the claim that sequential simulator construction and modification are error prone.

# 2.5 Prognosis

The examples and data presented demonstrate that manually mapping a concurrent, structural microarchitecture to a *correct* sequential program can be quite difficult. Others have noted that there is a problem with the accuracy of simulators, but disagree on the source of the problems [Desikan et al. 2001; Cain et al. 2002; Gibson et al. 2000]. We contend that the mapping problem is the fundamental cause of inaccuracies in and long development times of sequential simulators.

While validation may seem like an attractive solution to the problem of sequential simulator accuracy, validating a sequential simulator will further lengthen simulator development times. Furthermore, for a novel design, it is difficult to determine if a simulator is correct since no "golden" reference exists and the simulator is difficult to understand.

Unfortunately, no obvious technique to rapidly hand-craft correct sequential simulators has been proposed to date. A number of authors have proposed architecture description languages (ADLs) as an alternative means of modeling [Halambi et al. 1999; Pees et al. 1999; Siska 1998]. Unfortunately, these languages can only be used for processor modeling, and even within that domain the tools are generally inadequate. The systems either suffer from the mapping problem or limit the class of processors that can be modeled [Vachharajani et al. 2002].

Fortunately, the intuition and the results from the presented experiments indicate that models designed using a general-purpose methodology which allows structurally composed concurrently executing components can prove effective. Some structural systems [Emer et al. 2002], however, still force functional composition for some inter-component computation while others [Önder and Gupta 1998; Mishra et al. 2001] suffer from limited models of concurrency [Vachharajani et al. 2002]. In other systems, building a component, validating it, and reusing it across many designs is a possibility. This improves both the speed of model construction and reduces sources of error. In the next few sections, existing modeling tools that use concurrency and structural composition will be surveyed and analyzed in order to determine how effectively their features support the creation and use of reusable components.

#### EXISTING TRUE CONCURRENT-STRUCTURAL APPROACHES

From the previous section, it is clear that a simulation system that avoids the mapping problem must be fully concurrent and support structural composition. This way the modeling methodology itself does not *prevent* the construction and use of reusable components. In practice, however, it is insufficient to simply not prevent component-based reuse; highlevel concurrent-structural modeling systems need to possess certain capabilities which

|                 | 1        | U         |                       | 2        |  |

|-----------------|----------|-----------|-----------------------|----------|--|

|                 |          |           | Concurrent-Structural |          |  |

|                 | Static S | tructural | OOP                   |          |  |

| Capability      | Theory   | Practice  | Theory                | Practice |  |

| Parameters      | yes      | yes       | yes                   | yes      |  |

| -Structural     |          |           | yes                   | yes      |  |

| -Algorithmic    | yes      | yes       | yes                   | yes      |  |

| Polymorphism    | yes      | yes       | yes                   | yes      |  |

| -Parametric     | yes      |           | yes                   | yes      |  |

| -Overloading    | yes      | yes       |                       |          |  |

| Static Analysis | yes      | yes       |                       |          |  |

| Instrumentation | yes      |           | yes                   |          |  |

|                 |          |           |                       |          |  |

Table IV. Capabilities of existing methods and systems.

enable component-based reuse [Swamy et al. 1995]. These capabilities include:

#### **Parameters**

The ability to customize component properties with user-specified values.

Structural Parameters. The ability to customize hierarchical structure with parameters. This allows existing components to be reused hierarchically to create a flexible component. Example: parameters controlling the mix of functional units and presence of bypass connections in a structurally specified reusable CPU core.

Algorithmic Parameters. the ability to inherit and augment the behavior of an existing component with an algorithm. Example: parameter specifying arbitration logic inside a bus arbiter component.

# **Polymorphism**

The ability to support reuse across varying data types.

Parametric Polymorphism. The ability to create and use component models in a data type independent fashion. Examples: queues, memories, and crossbar switches that can store or process any data type.

Component Overloading. The ability to select different component implementations to match different data types. Note that function overloading, in which argument types select a function's implementation, differs from component overloading, where port and connection types select a component's implementation. Example: automatic selection between floating point ALU implementation and integer ALU implementation based on connection data types.

#### **Static Analysis**

The ability to analyze the resulting concurrent-structural model for user convenience, verification, and simulator optimization. Example: type inference to automatically resolve polymorphic port types.

Instrumentation The ability to probe a model for dynamic behavior without modifying the internals of any component. This allows reuse across different model objectives. Examples: data collection, debugging, and visualization.

The following two subsections relate the above abilities to two existing modeling methodologies: static structural modeling and modeling with a concurrent-structural library in an object-oriented programming (OOP) language. These systems are true concurrentstructural systems and thus do not suffer from the mapping problem. The analysis in this

ACM Journal Name, Vol. V. No. N. Month 20YY.

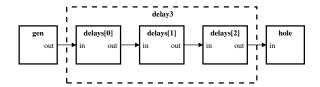

(a) Block diagram of a 3-stage delay chain specification.

(b) Block diagram of a flexible n-stage delay component.

Fig. 4. Block diagrams of chained delay components.

section will identify which of the above capabilities are supported in each of these methods and also highlight potential pitfalls present in these methods. The insight gained will guide the design of the Liberty Simulation Environment and its modeling language, the Liberty Structural Specification (LSS) language. Table IV can be used as a reference during the discussion.

# 3.1 Static Structural Modeling

Static structural modeling systems are concurrent-structural modeling systems that statically describe a model's overall structure. Models in these systems often resemble netlists of interconnected components, and typically these tools have drag-and-drop graphical user interfaces to construct models. Examples of such tools are Ptolemy II with the Vergil interface [Janneck et al. 2001] and HASE [Coe et al. 1998].

These systems support many of the features described above. Components typically export parameters so that they can be customized. Depending on the underlying language used to implement the components, a mechanism may exist to support algorithmic parameters via inheritance. Some systems support polymorphism [Janneck et al. 2001] and type inference to resolve the polymorphic types [Xiong 2002]. Models could even be instrumented using aspect-oriented programming (AOP) [Kiczales et al. 1997] to weave instrumentation code into the structure of the described model.

Unfortunately, the fact that these specifications are static implies a fundamental limitation of static structural modeling systems. Consider the structure shown in Figure 4(a). In static structural systems, one would explicitly instantiate the three blocks within the dotted box in the figure. However, this chain of blocks could not be wrapped into a flexible hierarchical component, as shown in Figure 4(b), where the length of the chain is a parameter since static structural systems provide no mechanism to iteratively connect the output of one block to the input of the next a parametric number of times. As a result, to permit flexibility, this simple hierarchical design would have to be discarded in favor of a more complex implementation of a primitive component implemented using a sequential

```

1

2

3

4

5

6

7

8

9

class delayn {

public InPort in;

public OutPort out;

Delav[] delavs;

delayn(int n) {

int i;

in=new InPort();

10

out=new OutPort();

11

12

delays=new Delay[n];

13

14

15

16

17

18

19

20

21

22

23

24

for(i=0;i<n;i++) {

delays[i]=new Delay();

in.connect(delays[0].in);

for(i=0;i<n-1;i++) {

delays[i+1]=new Delay();

delays[i].out.connect(delays[i+1].in);

delays[n-1].out.connect(out);

};

```

Fig. 5. Concurrent-structural OOP pseudo-code for an n-stage delay chain.

programming language. Implementing the primitive component for this simple example may not be difficult, but more complex examples, such as parametrically controlling the mix of functional units in a processor model, would require implementing a monolithic primitive processor component. This is tantamount to writing the whole simulator in a sequential programming language. Note that some static structural modeling systems may provide idioms for common patterns, such as chained connections. However, the fundamental lack of general mechanisms to parametrically and programmatically control model structure still remains. This deficiency ultimately restricts the flexibility of components built hierarchically and forces users to build large primitive components.

# 3.2 Modeling with Concurrent-Structural Libraries in OOP

A promising concurrent-structural modeling approach, such as the one taken by SystemC [Open SystemC Initiative (OSCI) 2001], which allows flexible primitive *and* hierarchical components, is to augment an existing OOP language with concurrency and a class library to support structural entities such as ports and connections. Objects take the place of components, and simulator structure is created at run-time by code that instantiates and connects these objects.

The basic features of object-oriented languages provide many of the capabilities described above. Object behavior can be customized via instantiation parameters passed to class constructors. Algorithmic parameters are supported via class inheritance. If the particular OOP language and the added structural entities support parametric polymorphism, then type-neutral components can be modeled as well.

Since component instantiation and connection occur at run-time, the OOP language's basic control flow primitives (i.e. loops, if statements, etc.) can be used to *algorithmically* build the structure of the system. This code can be encapsulated into an object and the internal structure can be easily controlled by structural parameters thus producing *flexible* hierarchical components. For example, the *n*-cycle delay component (Figure 4(b)) seen in

ACM Journal Name, Vol. V, No. N, Month 20YY.

the last section could be built by composing n single-cycle delay components as shown in the pseudo-code in Figure 5.

Unfortunately, run-time composition of structure provides component flexibility by precluding static analysis of model structure. This makes using these flexible components cumbersome. For example, any parametric polymorphism must be resolved via explicit type instantiation by the user, since the constraints used in type inference are obtained from the model's structure, which is unavailable at compile time. Ideally connecting the output of a floating point register file to an overloaded ALU should automatically select the ALU implementation that handles floating point data. However, this component overloading is not possible since the user must codify the particular ALU implementation in the instantiation statement rather than the compiler automatically determining this based on connectivity. Additionally, all component parameters, particularly those that control structure, must be explicitly specified by the user since the compiler is unable to automatically infer these values by analyzing the structure of the machine statically. Finally, implementing instrumentation that is orthogonal to machine specification is at best cumbersome. Powerful techniques such as aspect-oriented programming cannot be used since the desired join points (locations where instrumentation code should be inserted) are often parts of the model structure that is not known until run time. In addition to burdening the user, this lack of static analysis prevents certain key optimizations that can increase simulator performance. These optimizations can provide as much as a 40% increase in simulator performance (see Section 10), eliminating performance loss due to reuse. In practice, simulator performance penalties combined with these reuse burdens encourage users to build design-specific components that are fast and easy to use but enjoy little to no reuse due to their inflexibility.

# 3.3 Mixed approaches

A few approaches share some features of static structural models and some features of concurrent-structural OOP-based modeling. For example, VHDL allows limited algorithmic specification of structure via its generate statements and supports static analysis but does not support any of the other needed capabilities such as polymorphism and algorithmic parameters. The Balboa [Doucet et al. 2002] modeling environment supports algorithmic specification and component overloading by running type inference at runtime. However, Balboa and its type inference algorithm do not support parametric polymorphism [Doucet et al. 2003]. As we will see in the next section, the Liberty Simulation Environment gains, in practice, the full benefits of both static structural modeling and concurrent-structural OOP modeling.

# 3.4 Control Abstraction

Up to this point, this section focused on identifying the reuse-enabling features present in existing systems. However, facilitating rapid accurate modeling requires that a system also provide mechanisms for simplifying parts of a design that do not benefit from reuse. As was mentioned earlier, the global nature of control in a hardware design makes the components that manage control unlikely candidates for reuse. Existing systems, in addition to lacking some features to enable low-overhead reuse, also lack abstractions to simplify the task of describing control. Since the majority of components in these systems are not reused, having abstractions to reduce control specification overhead seems unnecessary; implementing components from scratch is the norm. Conversely, since components built

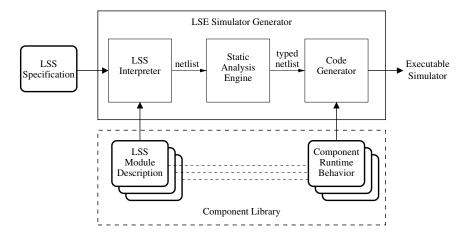

Fig. 6. Overview of the simulator generation process in LSE.

in the Liberty Simulation Environment are reusable, the need for control abstraction becomes more apparent. Section 6 will discuss the abstraction used in LSE.

#### 4. THE LIBERTY SIMULATION ENVIRONMENT

The Liberty Simulation Environment (LSE) is a fully concurrent-structural modeling framework designed to maximize reusability of components while minimizing specification overhead. A user models a machine in LSE by writing a machine description in the Liberty Structural Specification (LSS) language. This description specifies the instantiation of components, the customization of the flexible reusable components, and the interconnection of component ports. LSE includes a simulator generator that transforms this concurrent-structural machine description into an executable simulator and additional tool chains for other purposes, such as model visualization.

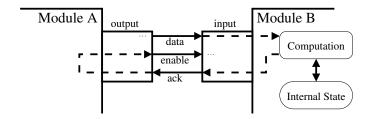

To avoid the mapping problem, LSE only allows components to communicate structurally, but this structure, along with component customizations, can be specified algorithmically via imperative programming constructs. Using these constructs, a model's structure can be built using code similar to the concurrent-structural OOP code in Figure 5. However, unlike modeling in concurrent-structural OOP, the LSS code only describes the model's structure and *not* its run-time behavior. Thus, as shown in Figure 6, the LSS description can be executed at *compile time* to generate the system's static structure. This allows model structure to be used for compile-time static analysis. Currently, LSE analyzes this structure to reduce specification overhead (described in Sections 8 and 9) and to optimize the built simulator performance (described in Section 10).

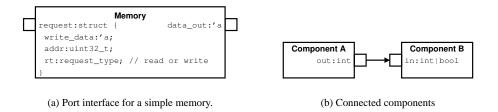

Each component in a model built using LSE is instantiated from a component template, called a *module*, that is analogous to a class in a concurrent-structural OOP system. The body of an LSS module specifies a component's parameterization interface, communication interface, and constructor. There are two types of modules in LSS. The first, *leaf modules*, are simple modules defined without composing behavior from other modules. The other style, *hierarchical modules*, are more complex modules obtaining their behavior through the composition and customization of existing modules. The next two sections will describe leaf and hierarchical modules and their parameterization.

```

module delay {

234567

parameter initial_state = 0:int;

instance d1:delay;

inport in:int;

instance d2:delay;

3

4

outport out:int;

dl.initial_state = 1;

tar_file="corelib/delay.tar";

5

d1.out -> d2.in;

8

BSL specific parameters here

10

(b) Sample use of the delay module.

```

(a) LSS module declaration for a leaf delay element.

Fig. 7. Delay element declaration and use.

#### 4.1 Leaf Modules

Leaf modules are simple modules whose behavior is externally specified. The module declaration is responsible for declaring the parameterization and communication interface of the module and for specifying where the module's behavior can be found. Figure 7(a) shows the declaration of a leaf module named delay. Line 2 in the figure declares a module parameter named initial\_state with type int and assigns the parameter a default value of 0. Lines 4 and 5 illustrate defining the communication interface of the module. These two lines define an input port named in and an output port named out, respectively, both with type int. Line 7 specifies where the code defining the run-time behavior of instances of this module can be found.

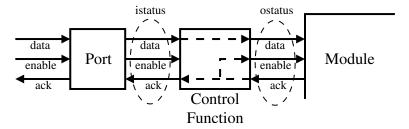

The code which defines a leaf module's behavior is not written in LSS, but a separate behavior specification language (BSL)<sup>5</sup>. A leaf module's behavior code specifies how values arriving on input ports are combined with internal state to produce values on the instance's output ports. The module behavior code uses the user specified values of module parameters to customize the behavior of a particular instance.

Figure 7(b) shows an example of instantiating and parameterizing the delay module. Lines 1 and 2 each instantiate the delay module to create module instances named d1 and d2 respectively. Line 4 gives the initial\_state parameter on instance d1 the value 1. Line 5 connects the output of d1 to the input of d2. Notice that the initial\_state parameter on instance d2 is not set. When such assignments are omitted, the parameter takes on its default value as defined in the module body (line 2 of Figure 7(a)).

Notice from the example that parameters in LSS are referenced nominally and can be specified *after* the instantiation statement (e.g. initial\_state is referenced on line 4 of Figure 7(b)) rather than in an a positional argument list as part of the instantiation statement. These choices were made because flexible modules typically have many parameters. Nominal parameter references clarify models since parameter names describe the parameter's purpose better than position in an argument list. Similarly, flexible placement of parameter assignment allows groups of related parameter assignments for different module instances to be co-located rather than scattered based on where modules are instantiated. Both features make using flexible components (i.e. those with many parameters) easier, encouraging their construction and use.

<sup>&</sup>lt;sup>5</sup>Currently, LSE uses a stylized version of C as the BSL, but the LSS language and the techniques presented in this paper are not dependent on the specific BSL used.

Fig. 8. Hierarchical component composition.

#### 4.2 Hierarchical Modules

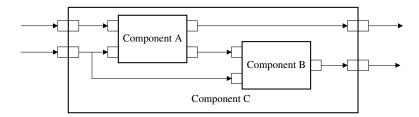

In addition to leaf modules, LSS supports the creation of complex modules by composing the behavior of existing modules into new *hierarchical* modules. Hierarchical modules, just like leaf modules, define a parameterization and communication interface by declaring ports and parameters. However, unlike leaf modules, the behavior of the module is specified by instantiating modules and connecting these sub-instances to the new module's input and output ports (see Figure 8). These module sub-instances execute *concurrently* and define the hierarchical module's behavior.

#### 5. LOW-OVERHEAD REUSE IN LSE

This section gives an overview of LSE's features that allow for easy reuse of flexible components. When discussing LSE features, the text highlights challenges in the features' implementation. Later sections will discuss the details of technology developed to address these challenges.

#### 5.1 Structural Parameters

Recall from Section 3 that to fully enable reuse, a modeling system needs to support parameters that control the structure of hierarchical modules. LSS allows the use of imperative control flow constructs to guide the sub-component instantiation, parameterization, and connection. *Any* parameter can be used to control these constructs; therefore all LSS parameters can be used as structural parameters.

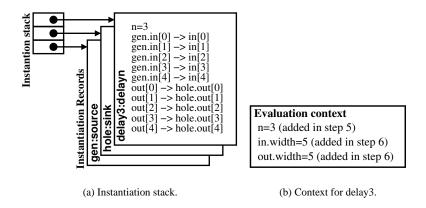

To see how a parameter can be used to control structure, consider the LSS code shown in Figure 9(a). This code defines a module that models an arbitrary depth delay pipeline (Figure 4(b)) built using single-cycle delay modules. The module delayn declares a single parameter n (line 2) which controls the number of stages in the pipeline. Anywhere after this declaration, the body of the module can read this parameter to guide how subinstances will be created, connected, or parameterized.

Lines 7 and 8 create an array of instances of the delay module that will be named delays in the BSL. Notice that the length of the array (the value enclosed in brackets on Line 8 of the figure) is controlled by the parameter n.

Lines 12 through 16 connect the delay instances in a chain as shown in Figure 4(b). Notice how the general purpose C-like for-loop causes the length of the connection chain to vary with the parameter n.

Figure 9(b) shows how the delayn module can be used to create a 3-stage delay pipeline. The module is instantiated on line 3, its n parameter is set on line 5, and finally the instance is connected on lines 7 and 8. The block diagram of the resulting system

ACM Journal Name, Vol. V, No. N, Month 20YY.

```

module delayn {

2

3

4

parameter n:int;

inport in:int;

5

outport out:int;

instance gen:source;

67

instance hole:sink;

var delays:instance ref[];

instance delay3:delayn;

8

9

delays=new instance[n](delay, "delays");

4

delay3.n=3;

10

var i:int;

6

7

gen.out -> delay3.in;

12

13

in -> delays[0].in;

8

delay3.out -> hole.in;

for(i=1;i<n;i++) {

14

15

delays[i-1].out -> delays[i].in;

(b) Use of delayn, n=3

delays[n-1].out -> out;

```

(a) The LSS module declaration.

Fig. 9. n-stage delay chain declaration and use.

is the same as in Figure 4(a).

#### 5.2 Extending Component Behavior

Section 3 also stated that a system that supports reuse must support algorithmic parameters to allow an existing component's behavior to be extended or augmented. In LSE, these algorithmic parameters are called *userpoints*. Userpoints accept string values whose content is BSL code that forms the body of a function invoked by a module's behavioral specification to accomplish some computation or state-update task. The function signature, the arguments it receives and the return type it must produce, is defined by the data type of the userpoint. Just like other parameters, userpoint parameters can have default values, thus allowing the module to define default behavior which can be overridden by the user.

In concurrent-structural OOP systems, inheritance takes the place of algorithmic parameters. Just like algorithmic parameters, inheritance allows a component's behavior to be modified or extended. However, a single userpoint parameter assignment on a module instance is the concurrent-structural OOP equivalent of inheriting a class, overriding a virtual member function, and then instantiating the inherited class. Thus userpoints dramatically reduce the overhead of one-off inheritance (i.e. inheriting a module and instantiating it once). Since one-off inheritance is common in structural modeling, using userpoints rather than inheritance reduces specification overhead. More formal styles of inheritance can be achieved via userpoint assignment and hierarchical module construction.

To allow userpoints to maintain state across multiple invocations, LSS also allows the state of a module instance to be extended. State is added by declaring *run-time variables* (i.e. variables available during simulation rather than during model compilation). To allow this state to be initialized and *synchronously* updated, LSE provides on every instance the predefined userpoints init and end\_of\_timestep, which are invoked at the beginning of simulation and the end of each clock cycle respectively<sup>6</sup>.

<sup>&</sup>lt;sup>6</sup>These userpoints are altered when modeling multiple clock domains in LSE.

```

module delayn {

2

3

4

parameter n:int;

inport in: 'a;

5

outport out: 'a

6

7

if(in.width != out.width)

8

9

punt("in.width must match out.width");

instance gen:source;

10

var delays:instance ref[];

2

instance hole:sink;

delays=new instance[n](delay, "delays");

instance delay3:delayn;

var i:int;

13

5

delay3.n=3;

14

15

/* The LSS_connect_bus(x,y,z)

* built-in does:

LSS connect bus(gen.out,

16

17

delav3.in, 5);

for(i=0; i<z; i++) { x[i]->y[i]; }

LSS connect bus(delay3.out,

18

19

20

21

22

23

24

25

26

10

hole.in. 5);

LSS connect bus(in,delays[0].in,in,width);

in -> delays[0].in;

(b) Use of the modified delayn module.

for(i=1;i<n;i++) {

LSS_connect_bus(delays[i-1],

delays[i].in,in.width);

LSS_connect_bus(delays[n-1],out,in.width);

```

Fig. 10. Modified delayn module and a sample use.

# 5.3 Flexible Interface Definition

connections.

(a) Modified delayn module that supports multiple port

To maximize the flexibility of components, LSS extends parametric control of structure to include parametric control of interfaces as well. A common use of this facility is parametric control of interface size, such as the number of read ports on a register file. However, as will be seen, this customization can control any portion of the module's interface.

5.3.1 Flexible Interface Size. To facilitate scalable interfaces such as a register file with a customizable number of read ports, each port in LSS is actually a variable length array of port instances. Rather than connecting two ports together to have two instances communicate, one connects two port instances together. For each port in a module, the port's width (the number of connections made to the port) is available as a parameter for use in a module's body. These width parameters are automatically set by counting the number of connections actually made to a particular port. This automatic inference of port width greatly simplifies specifications. Without this inference, users would have to manually keep the width parameters consistent with the connections. This process would be prone to error, and fixing the errors would be tedious, time-consuming, and unnecessary.

Figure 10 illustrates how one would use these scalable interfaces to build a hierarchical module, and it also demonstrates how a port's width parameter is automatically set. Recall the delayn module presented in Figure 9. While the delay module (which was used to build the delayn module) supports multiple connections to its in and out ports, the delayn module internally connects only one port instance to the chain of delay modules. If a connection were made to more than one port instance of either port on the delayn module, it would be ignored since it is internally unconnected.

Fig. 11. Use-based specialization exporting additional parameters

Figure 10(a) shows the delayn module extended to support connections to multiple port instances, and Figure 10(b) shows a sample use of the module. Notice that many connections are now made from the the in port to the head of the delay chain (line 19 of Figure 10(a)), between delay elements in the chain (lines 22-23), and finally from the tail of the chain to the out port (line 25). Further, notice that the number of connections made is controlled by the parameter in.width, yet this parameter has no explicit default value or user assignment. Instead, its value is inferred by the system based on the number of connections made. In this example, since five connections are made to the in port (lines 7-8 of Figure 10(b)), the parameter would have the value 5.

5.3.2 Parameterized Interface Definition. The inference of the width parameter described above is an example of an LSS feature called *use-based specialization*. This feature allows a module's context (its parametericity and connectivity) to alter its behavior and its interface. In the above example, only the widths of ports were varied, but use-based specialization can be used to alter *any* piece of the a module's interface. For example, by detecting whether a branch\_target port is connected, a branch prediction module can infer whether or not it should also implement BTB (branch target buffer) functionality. If BTB functionality is necessary, the component can export additional parameters and ports to further customize this behavior.

To see how use-based specialization can affect a hierarchical component's interface and structure, consider the code in Figure 11. Here the module infers whether an internal arbiter is necessary by comparing the width of its input port to that of its output port. If the input port is wider than the output port, an arbiter is instantiated, and a userpoint parameter is exported so that the arbitration policy can be parametrically specified.

Notice that the module's interface can change *after* it has been instantiated and used. In the example, the module's connectivity, which is determined after instantiation, controls whether the module will have a certain parameter. Without use-based specialization, the module's interface would be fixed at instantiation, and the arbitration\_policy parameter would always exist. If the parameter has no default value, then the user would be forced to set it, even when no arbitration is necessary. Alternatively, the parameter could be assigned a default value. However, since there are many possible default arbitration policies, having the module quietly make this important design decision when widths are changed is undesirable. While this is less severe than the problem illustrated in Figure 3 since the arbiter is explicitly created and its behavior determined only by microarchitec-

tural state, a design decision is nonetheless being made without user knowledge. Use-based specialization makes deciding whether the parameter ought to have a default value unnecessary by providing the best of both worlds; the user must provide the policy when it is necessary and is not forced to provide it when it is not.

While use-based specialization reduces the overhead of using flexible components by automatically tailoring components to their environment, it introduces complications into the execution of LSS. Since a module's parameterization and connectivity can affect its interface, the module's interface is not known until after its parameters have been set and its ports connected. However, this parameterization and connection relies on the interface being known. To resolve this apparent circularity, LSS uses novel evaluation semantics that will be presented in Section 8.

# 5.4 Polymorphic Interfaces

In addition to flexible interface definitions, LSE also supports modules with polymorphic interfaces. LSS supports two types of polymorphism: parametric polymorphism and component overloading.

5.4.1 Parametric Polymorphism. Parametric polymorphism allows for the creation of data type independent components. This feature is particularly useful for reusable communication primitives like routers, arbiters, and filters, and for reusable state elements like buffers, queues, and memories.

As an example, recall the delayn module shown in Figure 9(a). As shown, the delayn module can only handle the int data type since the ports are created with type int (lines 4 and 5 in Figure 9(a)). However, the behavior of the module, creating a delay pipeline that is n stages deep, is independent of data type. Consequently, the delayn module is an ideal candidate for using parametric polymorphism. To make the module parametrically polymorphic, rather than making the in and out ports have the data type int, one would declare the ports' types using type variables as shown below:

```

4 inport in: 'a;

5 outport out: 'a;

```

The type 'a is a type variable (all type variables in LSS begin with a ') which can be instantiated with any LSS type. This flexibility makes the modified delayn module data type independent<sup>7</sup>. Since the in and out ports use the same type variable, both ports must have the same concrete type. This guarantees that the type of data entering the delay pipeline is consistent with the type of data that comes out. While this example demonstrates parametric polymorphism on a hierarchical component, it can also be used on leaf components. In such cases, the BSL code for the leaf component is specialized based on the concrete type given to all type variables.

5.4.2 Component Overloading. Component overloading is useful when defining a component that supports more than one data type on a particular port, but needs to be customized based on which type is actually used. Component overloading is supported with disjunctive types. A disjunctive type, denoted as type1 | type2 in LSS, specifies that the entity with this type may statically have type type1 or type2, but not both simultane-

$<sup>^7</sup>$ This modification to delayn assumes that the delay module also uses parametric polymorphism. The delay module defined in the LSE core module library does, in fact, support this.

```

1 module ALU {

2    inport in1:(int | float)

3    inport in2:(int | float)

4    outport result: (int | float)

6    constrain ''in1 == ''in2;

8    constrain ''in1 == ''result;

9    ...

10 };

```

Fig. 12. An overloaded ALU module interface.

ously<sup>8</sup>. Depending on which type is actually selected, a different module implementation will be selected.